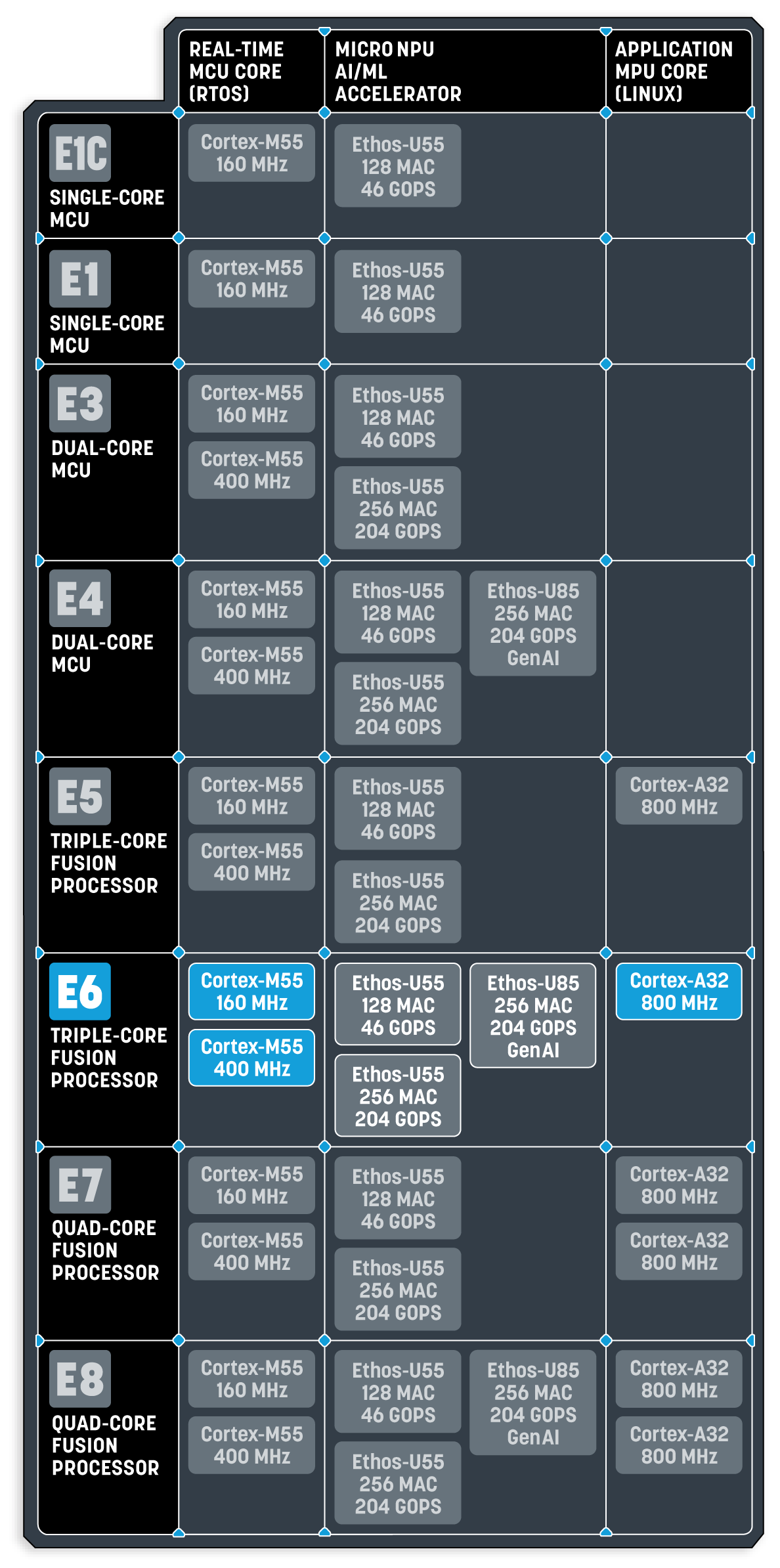

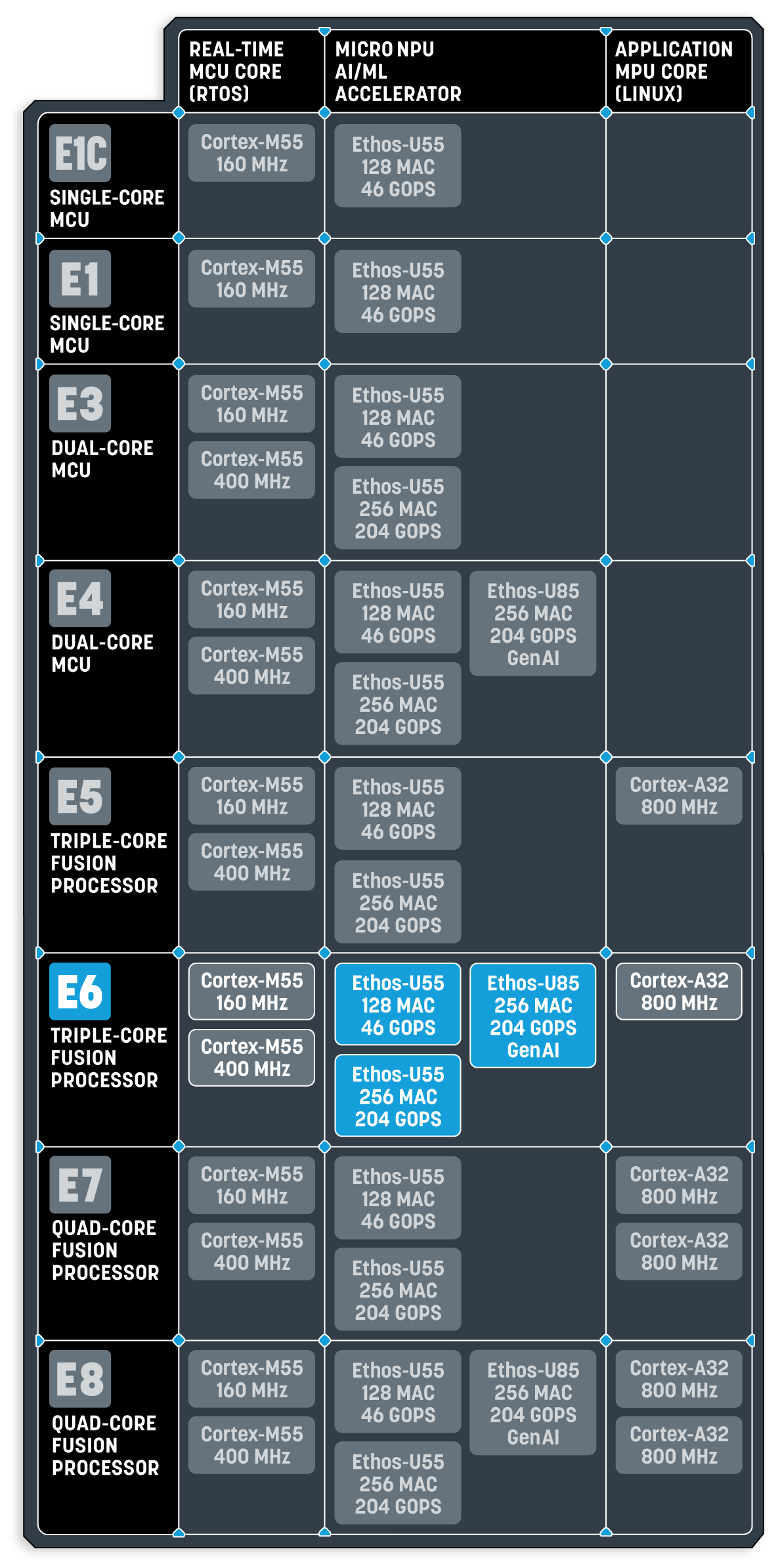

Tri-Core GenAI Fusion Processor

The Ensemble E6 series represents a new category of embedded controllers that fuse MPU, MCU, and AI/ML capabilities into a single device. It features dual Cortex-M55 CPUs—one optimized for power efficiency and the other for high-performance compute—alongside a Gen-AI enabled Ethos-U85 and dual Ethos-U55 NPUs to deliver robust AI/ML acceleration. A Cortex-A32 application processor enables support for high-level operating systems like Linux. This powerful combination makes the E6 series ideal for advanced edge applications such as home automation, smart lighting, security cameras, and industrial control systems.

Key Benefits of E6:

-

Linux & RTOS for efficient balance of application and real-time processing

-

Single chip imaging pipeline with up to 2 MIPI-CSI camera interfaces + Hardware ISP & image compression capabilities

-

Rich user interface with hardware accelerated graphics, hi-perf networking

E6 Specifications

- Arm Cortex®-A32 Core with Arm Neon™ SIMD Extension up to 800 MHz, 512KB Shared L2, 32KB L1 Instruction and Data Caches, MMU, Armv8-A ISA with Arm TrustZone®

- High-Performance Arm® Cortex®-M55 Core, up to 400 MHz, with Helium™ Vector Processing Extension, Double-Precision FPU, 1.25MB SRAM 0-wait State Tightly- Coupled Memory, 32KB Instruction and Data Caches, Armv8.1-M ISA with Arm TrustZone®, and 4.37 CoreMark®/MHz Performance Benchmark

- High-Efficiency Arm® Cortex®-M55 Core, up to 160 MHz, with Helium™ Vector Processing Extension, DoublePrecision FPU, 512KB of SRAM 0-wait State Tightly Coupled Memory, 32KB Instruction and Data Caches, Armv8.1-M ISA with Arm TrustZone®, and 4.37 CoreMark®/MHz Performance Benchmark

- High-Performance 400-MHz 64-bit AXI Bus Fabric Common Across All CPUs

- 1× Arm Ethos™-U85 Neural Processing Unit (NPU) for Generative AI (NPU-HG), 256 MAC/cycle up to 400 MHz and 204 GOPS, Supporting Recurrent Neural Networks (RNN), Convolutional Neural Networks (CNN), and Transformer Networks, Fed by 128-bit wide High-Bandwidth Local Memory at over 12 GB/s

- 2× Arm Ethos™-U55 Neural Processing Units— 1× 256 MAC/cycle up to 204 GOPS, 1× 128 MAC/cycle up to 46 GOPS, On-the-Fly Weight Decompression with Dedicated DMA Controller

- More than 800× Performance Uplift from Cortex-M4 for Inference Time

- Over 76× Less Energy Consumed when Using Ethos-U85 together with Cortex-M55

- Autonomous Intelligent Power Management (aiPM™)

- FD-SOI Low Leakage Process

- 1.3 µA Consumed in STOP Mode with LPRTC, LPTIMER, LPCMP, BOR, 4KB Utility SRAM, Wake Pins

- As Low as 27 µA/MHz Dynamic Consumption for High-Efficiency Cortex-M55

- Multiple Power Domains, Dynamic Power, Gating, Voltage and Clock Scaling, DC-DC Converter

- High Endurance MRAM Non-Volatile Memory

- Up to 5.5MB

- SRAM

- 9.75MB total SRAM: 8MB Bulk + 1.25MB M55-HP TCM + 0.5MB M55-HE TCM

- Optional Data Retention of Bulk SRAM and M55-HE TCM SRAM Contents

- 4KB Always-On Utility SRAM

- 2× 16-bit Hex SPI, each up to 400 MB/s SDR, 800 MB/s DDR, with Inline AES Decryption and Support for XIP and HyperBus

- 1× SD® v4.2, eMMC™ v5.1 Channel with DMA

- Hardware-based Root-of-Trust (RoT) with Unique Device ID

- Secure Key Generation and Storage, Secure Certificate Storage

- Factory-provisioned Private Keys

- Crypto Accelerators—AES (up to AES-256), ECC (up to 384 bits), SHA (up to SHA-256), RSA (up to RSA-3072), and NIST compliant TRNG

- Secure Debugging with Certificate Authentication

- 12× Universal High-Resolution 32-bit Timers

- Capable of Motor and LED Lighting Control

- 3× Low-Power Universal High-Resolution 32-bit Timers

- 4× Watchdog Timers

- 4× Low-Power 32-bit Timers

- 1× Real-Time Counter

- 4× Quadrature Encoder Counters

- Works in Tandem with ISP to Store Compressed

- Images and Motion JPEG (MJPEG) Video Clips

- Maximum Performance: 2MP at 200 FPS

- Input Formats: YUV400, YUV420, YUV422, RGB

- Supports JPEG ISO/IEC 10918-1, ITU-T T.81

- Supports MJPEG T.81 Format

- Encoding Color Space: YUV 4:0:0, 4:2:0, 4:2:2

- Cropping, Rotation, Padding

- 1× 10/100 Ethernet with DMA

- 1× USB 2.0 HS/FS Host/Device with DMA

- 1× SDIO v4.1 Channel with DMA

- 1× CAN FD Channel up to 10 Mbps

- 1× MIPI® I3C® Channel

- 4× I2C Channels up to 3.4 Mbps Throughput

- 2× Low-Power I2C Channel

- 8× UART Channels up to 2.5 Mbps (4× with RS485 Driver Control)

- 1× Low-Power UART Channel

- 4× SPI Channels up to 50 Mbps Throughput

- 1× Low-Power SPI Channel

- 3× 12-bit ADC (18 Single-Ended Inputs)

- 1× 24-bit ADC (4 Differential Inputs)

- Programmable Gain Instrumentation Amplifier (1× to 128×)

- 2× 12-bit DACs (2 channels)

- 4× High-Speed Analog Comparators with 2.5-ns Response (16 Inputs)

- 1× Low-Power Analog Comparator (4 Inputs)

- Internal Temperature Sensor

- Internal Precision Reference Voltage

- 1× 2-Lane MIPI D-PHY CSI-2®, 2.5 Gbps each lane

- Option for 2× MIPI D-PHY CSI-2 Interface by using the MIPI D-PHY DSI in Slave Mode. Allows Interleaving Two Image Streams from Two Separate Image Sensors

- 1× Camera Parallel Interface (CPI), up to 16 bits

- 1× Low-Power CPI, up to 8 bits

- Clocked up to 400 MHz, 64-bit Bus Connection

- Maximum Input/Output Resolution: 2MP (1920 × 1080)

- Configurable Frame Rate Control: 1 to 60 FPS Input Monochrome Formats: 8-bit, 10-bit

- Conversions: Demosaic Bayer to RGB, YUV422 to YUV444 to RGB

- Output Formats: 8-bit Monochrome, RAW 8/10/12-bit with Raster Scanning, RGB888 Planar, YUV, Y-only

- Auto White Balance and Auto Exposure

- Gamma Correction

- Crop, Scale, Binning, Black Level, Gain

- Graphics LCD Controller

- 1× Display Parallel Interface (DPI), up to 24-bit RGB

- 1× 2-Lane MIPI D-PHY DSI®, 2.5 Gbps each lane

- D/AVE 2D Graphics Processing Unit

- 4× I2S Synchronous Stereo Audio Interfaces

- 1× Low-Power I2S Stereo Audio Interface

- 4× 2-channel Pulse Density Modulation (PDM) Microphone Inputs (8 Mono Microphones)

- 4× 2-channel Low-Power Pulse Density Modulation (LPPDM) Microphone Inputs (8 Mono Microphones)

- Up to 136× 1.8-V GPIOs (Shared with Peripherals)

- Up to 8× Selectable 1.8-V to 3.3-V GPIOs (Shared with Peripherals)

- LFRC – Internal Low-Frequency RC Oscillator (32.7 kHz, ±4%)

- HFRC – Internal High-Frequency RC Oscillator (Up to 76.8 MHz, ±2%)

- LFXO – External Low-Power Crystal Oscillator or Quartz Crystal (32.768 kHz)

- HFXO – External High-Frequency Crystal Oscillator or Quartz Crystal (24 MHz to 38.4 MHz)

- One Fractional-N PLL to Generate System Clock, Additional Fractional-N PLL to Generate Audio Clock

- Global Event Mapping to Configurable Triggers

- 3× 32-Channel General DMA Controllers

- CRC Calculation Accelerator with Programmable Polynomials

- Programmable Low Supply Voltage Detect Warning (Brown-Out Detect)

- Power-On Reset and Brown Out Reset

- Real-Time Clock

- JTAG/SWD Debug Interface

- 1.75 V to 4.8 V Primary Supply Range

- 1.08 V to 1.98 V I/O Supply Range (1.8 V I/O)

- 3.0 V to 4.0 V I/O Supply Range (3.3 V Flex I/O)

- -40 °C to 75 °C Extended Ambient Temperature Range

- -40 °C to 105 °C Extended Junction Temperature Range

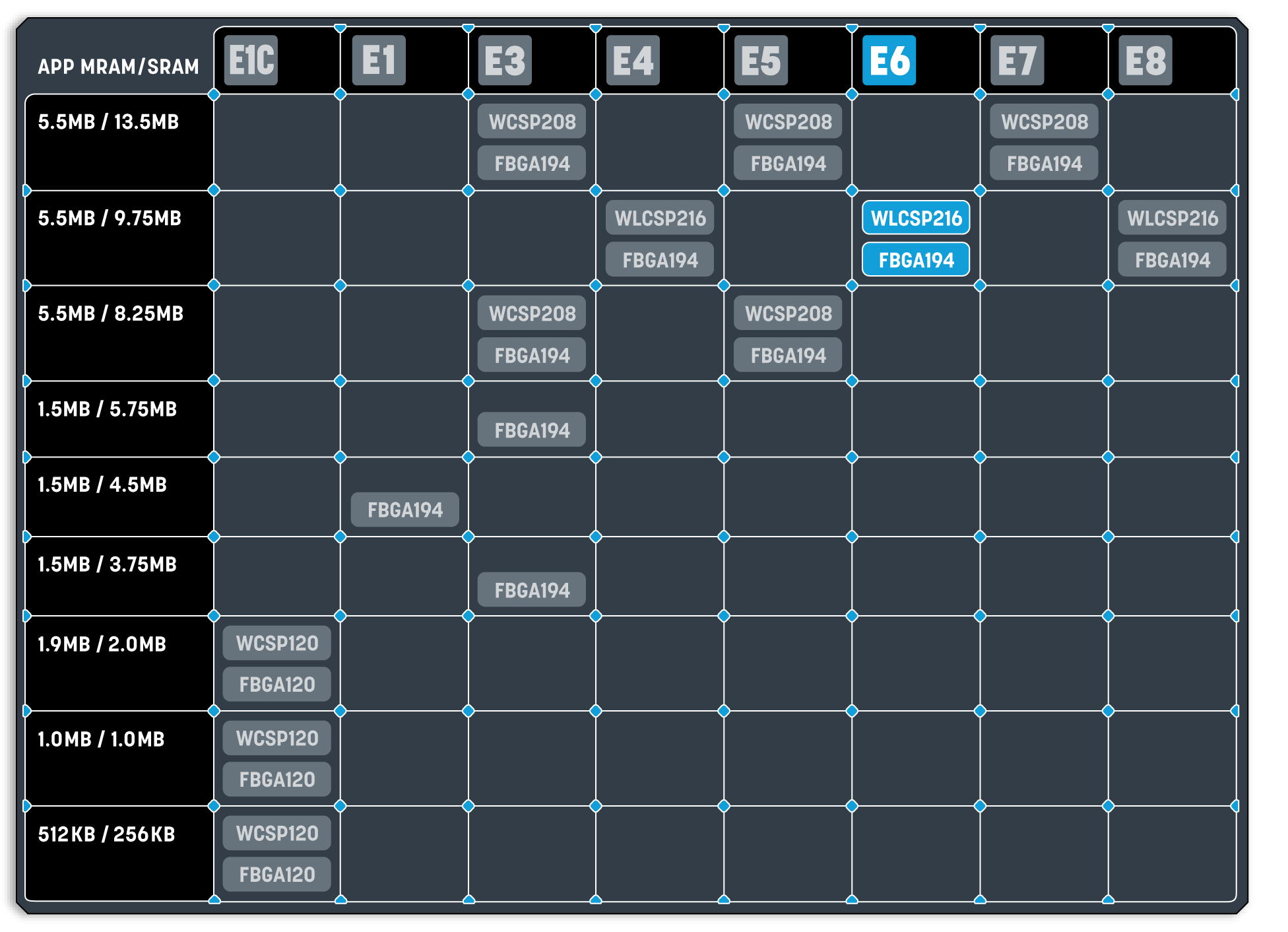

- WLCSP216, 0.4 mm Pitch

- FBGA194, 0.5 mm Pitch

High-Performance Tri-Core Fusion Processor

- Arm Cortex®-A32 Core with Arm Neon™ SIMD Extension up to 800 MHz, 512KB Shared L2, 32KB L1 Instruction and Data Caches, MMU, Armv8-A ISA with Arm TrustZone®

- High-Performance Arm® Cortex®-M55 Core, up to 400 MHz, with Helium™ Vector Processing Extension, Double-Precision FPU, 1.25MB SRAM 0-wait State Tightly- Coupled Memory, 32KB Instruction and Data Caches, Armv8.1-M ISA with Arm TrustZone®, and 4.37 CoreMark®/MHz Performance Benchmark

- High-Efficiency Arm® Cortex®-M55 Core, up to 160 MHz, with Helium™ Vector Processing Extension, DoublePrecision FPU, 512KB of SRAM 0-wait State Tightly Coupled Memory, 32KB Instruction and Data Caches, Armv8.1-M ISA with Arm TrustZone®, and 4.37 CoreMark®/MHz Performance Benchmark

- High-Performance 400-MHz 64-bit AXI Bus Fabric Common Across All CPUs

Efficient Micro NPUs for AI/ML Acceleration

- 1× Arm Ethos™-U85 Neural Processing Unit (NPU) for Generative AI (NPU-HG), 256 MAC/cycle up to 400 MHz and 204 GOPS, Supporting Recurrent Neural Networks (RNN), Convolutional Neural Networks (CNN), and Transformer Networks, Fed by 128-bit wide High-Bandwidth Local Memory at over 12 GB/s

- 2× Arm Ethos™-U55 Neural Processing Units— 1× 256 MAC/cycle up to 204 GOPS, 1× 128 MAC/cycle up to 46 GOPS, On-the-Fly Weight Decompression with Dedicated DMA Controller

- More than 800× Performance Uplift from Cortex-M4 for Inference Time

- Over 76× Less Energy Consumed when Using Ethos-U85 together with Cortex-M55

Extreme-Low Power Technology

- Autonomous Intelligent Power Management (aiPM™)

- FD-SOI Low Leakage Process

- 1.3 µA Consumed in STOP Mode with LPRTC, LPTIMER, LPCMP, BOR, 4KB Utility SRAM, Wake Pins

- As Low as 27 µA/MHz Dynamic Consumption for High-Efficiency Cortex-M55

- Multiple Power Domains, Dynamic Power, Gating, Voltage and Clock Scaling, DC-DC Converter

On-Chip Application Memory

- High Endurance MRAM Non-Volatile Memory

- Up to 5.5MB

- SRAM

- 9.75MB total SRAM: 8MB Bulk + 1.25MB M55-HP TCM + 0.5MB M55-HE TCM

- Optional Data Retention of Bulk SRAM and M55-HE TCM SRAM Contents

- 4KB Always-On Utility SRAM

External Memory Interfaces

- 2× 16-bit Hex SPI, each up to 400 MB/s SDR, 800 MB/s DDR, with Inline AES Decryption and Support for XIP and HyperBus

- 1× SD® v4.2, eMMC™ v5.1 Channel with DMA

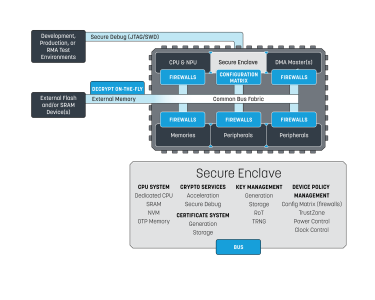

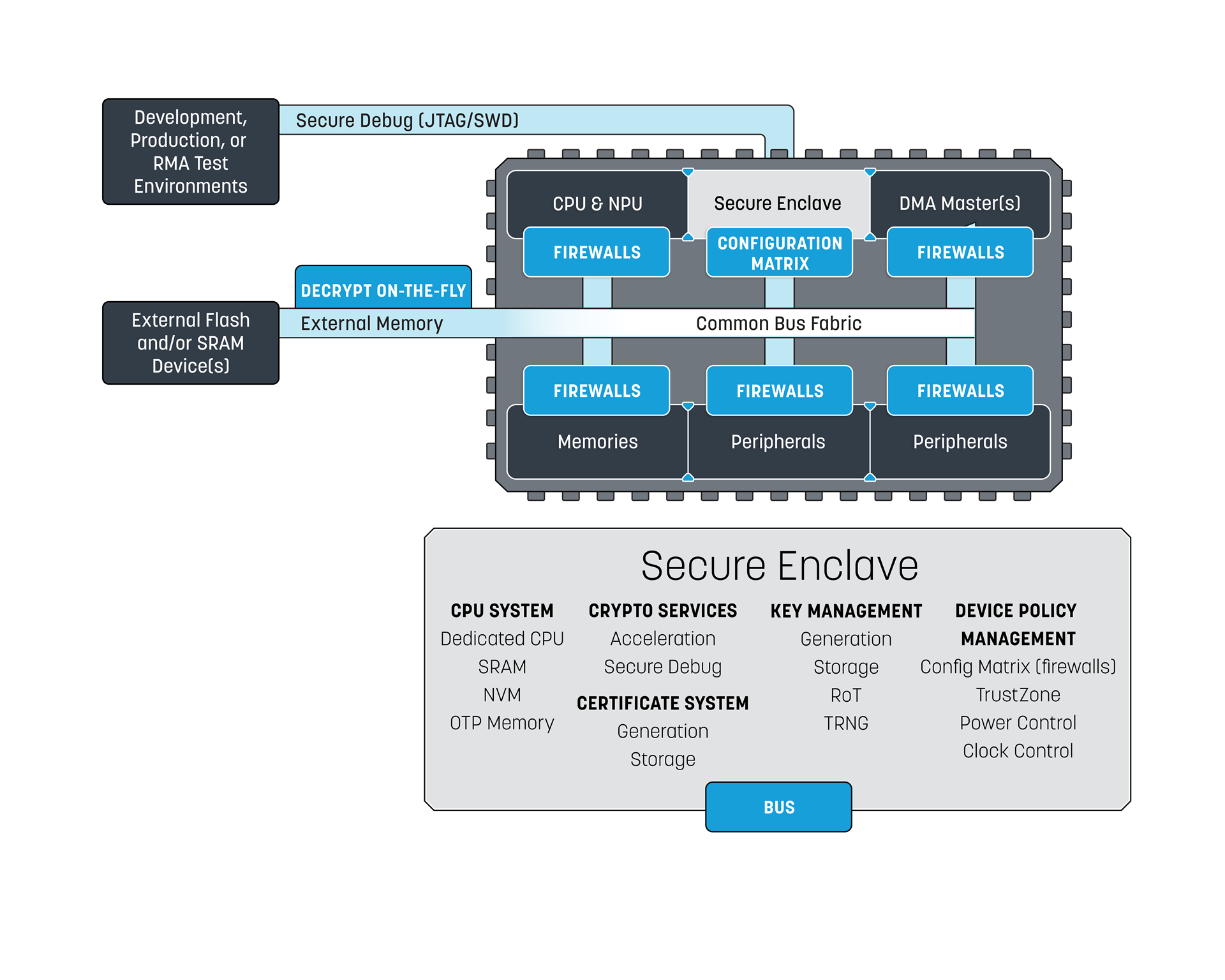

Secure Enclave

- Hardware-based Root-of-Trust (RoT) with Unique Device ID

- Secure Key Generation and Storage, Secure Certificate Storage

- Factory-provisioned Private Keys

- Crypto Accelerators—AES (up to AES-256), ECC (up to 384 bits), SHA (up to SHA-256), RSA (up to RSA-3072), and NIST compliant TRNG

- Secure Debugging with Certificate Authentication

Timing Control and Measurement

- 12× Universal High-Resolution 32-bit Timers

- Capable of Motor and LED Lighting Control

- 3× Low-Power Universal High-Resolution 32-bit Timers

- 4× Watchdog Timers

- 4× Low-Power 32-bit Timers

- 1× Real-Time Counter

- 4× Quadrature Encoder Counters

JPEG Encoder

- Works in Tandem with ISP to Store Compressed

- Images and Motion JPEG (MJPEG) Video Clips

- Maximum Performance: 2MP at 200 FPS

- Input Formats: YUV400, YUV420, YUV422, RGB

- Supports JPEG ISO/IEC 10918-1, ITU-T T.81

- Supports MJPEG T.81 Format

- Encoding Color Space: YUV 4:0:0, 4:2:0, 4:2:2

- Cropping, Rotation, Padding

Serial Communication Interfaces

- 1× 10/100 Ethernet with DMA

- 1× USB 2.0 HS/FS Host/Device with DMA

- 1× SDIO v4.1 Channel with DMA

- 1× CAN FD Channel up to 10 Mbps

- 1× MIPI® I3C® Channel

- 4× I2C Channels up to 3.4 Mbps Throughput

- 2× Low-Power I2C Channel

- 8× UART Channels up to 2.5 Mbps (4× with RS485 Driver Control)

- 1× Low-Power UART Channel

- 4× SPI Channels up to 50 Mbps Throughput

- 1× Low-Power SPI Channel

Analog Interface Capabilities

- 3× 12-bit ADC (18 Single-Ended Inputs)

- 1× 24-bit ADC (4 Differential Inputs)

- Programmable Gain Instrumentation Amplifier (1× to 128×)

- 2× 12-bit DACs (2 channels)

- 4× High-Speed Analog Comparators with 2.5-ns Response (16 Inputs)

- 1× Low-Power Analog Comparator (4 Inputs)

- Internal Temperature Sensor

- Internal Precision Reference Voltage

Camera Interfaces

- 1× 2-Lane MIPI D-PHY CSI-2®, 2.5 Gbps each lane

- Option for 2× MIPI D-PHY CSI-2 Interface by using the MIPI D-PHY DSI in Slave Mode. Allows Interleaving Two Image Streams from Two Separate Image Sensors

- 1× Camera Parallel Interface (CPI), up to 16 bits

- 1× Low-Power CPI, up to 8 bits

ISP Acceleration Unit

- Clocked up to 400 MHz, 64-bit Bus Connection

- Maximum Input/Output Resolution: 2MP (1920 × 1080)

- Configurable Frame Rate Control: 1 to 60 FPS Input Monochrome Formats: 8-bit, 10-bit

- Conversions: Demosaic Bayer to RGB, YUV422 to YUV444 to RGB

- Output Formats: 8-bit Monochrome, RAW 8/10/12-bit with Raster Scanning, RGB888 Planar, YUV, Y-only

- Auto White Balance and Auto Exposure

- Gamma Correction

- Crop, Scale, Binning, Black Level, Gain

Display Interfaces & Graphics

- Graphics LCD Controller

- 1× Display Parallel Interface (DPI), up to 24-bit RGB

- 1× 2-Lane MIPI D-PHY DSI®, 2.5 Gbps each lane

- D/AVE 2D Graphics Processing Unit

Audio Interfaces

- 4× I2S Synchronous Stereo Audio Interfaces

- 1× Low-Power I2S Stereo Audio Interface

- 4× 2-channel Pulse Density Modulation (PDM) Microphone Inputs (8 Mono Microphones)

- 4× 2-channel Low-Power Pulse Density Modulation (LPPDM) Microphone Inputs (8 Mono Microphones)

General Input/Output

- Up to 136× 1.8-V GPIOs (Shared with Peripherals)

- Up to 8× Selectable 1.8-V to 3.3-V GPIOs (Shared with Peripherals)

Clock Generation

- LFRC – Internal Low-Frequency RC Oscillator (32.7 kHz, ±4%)

- HFRC – Internal High-Frequency RC Oscillator (Up to 76.8 MHz, ±2%)

- LFXO – External Low-Power Crystal Oscillator or Quartz Crystal (32.768 kHz)

- HFXO – External High-Frequency Crystal Oscillator or Quartz Crystal (24 MHz to 38.4 MHz)

- One Fractional-N PLL to Generate System Clock, Additional Fractional-N PLL to Generate Audio Clock

System

- Global Event Mapping to Configurable Triggers

- 3× 32-Channel General DMA Controllers

- CRC Calculation Accelerator with Programmable Polynomials

- Programmable Low Supply Voltage Detect Warning (Brown-Out Detect)

- Power-On Reset and Brown Out Reset

- Real-Time Clock

- JTAG/SWD Debug Interface

Operating Parameters

- 1.75 V to 4.8 V Primary Supply Range

- 1.08 V to 1.98 V I/O Supply Range (1.8 V I/O)

- 3.0 V to 4.0 V I/O Supply Range (3.3 V Flex I/O)

- -40 °C to 75 °C Extended Ambient Temperature Range

- -40 °C to 105 °C Extended Junction Temperature Range

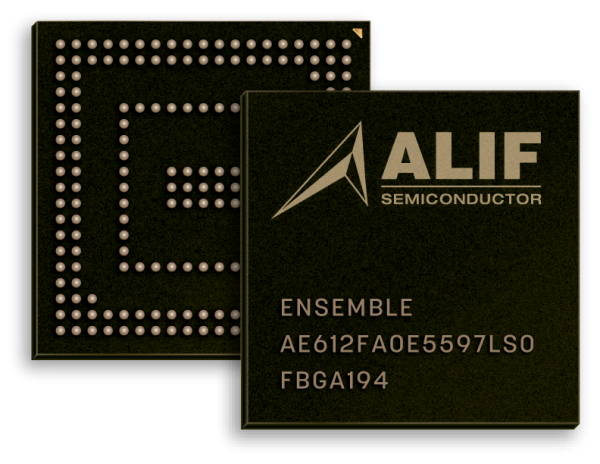

Packages

- WLCSP216, 0.4 mm Pitch

- FBGA194, 0.5 mm Pitch